565РУ6

565РУ6, 565РУ6В, 565РУ6Г, 565РУ6Д, КР565РУ6Б, КР565РУ6В, КР565РУ6Г, КР565РУ6Д

Описание

Микросхемы представляют собой динамическое оперативное запоминающее устройство емкостью 16384 бит (16кх1); для КР565РУ61Д, КР565РУ62Д емкостью 8 кбит (8кх1), со схемой управления. Содержат 74210 интегральных элементов. Корпус типа 2103.16-2, масса не более 2,5 г.

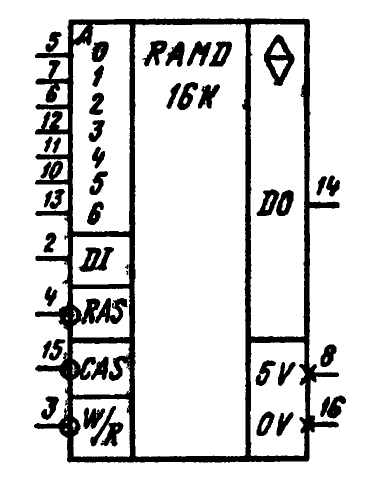

Условное графическое обозначение КР565РУ6

Условное графическое обозначение КР565РУ6

Назначение выводов

1, 9 - свободные

2 - информационный вход DI

3 - вход сигнала “запись-считывание" W/R

4 - вход сигнала выборки строк RAS

5 - адресный вход А0

6 - адресный вход А2

7 - адресный вход А1

8 - напряжение питания

10 - адресный вход А5

11 - адресный вход А4

12 - адресный вход А3

13 - адресный вход А6

14 - информационный выход D0

15 - вход сигнала выборки столбцов CAS

16 - общий.

Таблица истинности

| Входы | Выход | Режим работы | |||

| RAS | CAS | WR | DI | DO | |

| 1 | 1 | X | X | Z | Схема не выбрана (хранение) |

| 1 | 0 | X | X | Z | Схема не выбрана (хранение) |

| 0 | 1 | X | X | Z | Регенерация |

| 0 | 0 | 0 | 0/1 | Z | Запись 0/1 |

| 0 | 0 | 1 | X | 0/1 | Считывание |

Рекомендации по применению КР565РУ6

Допустимое значение статического потенциала 100 В. После распайки микросхемы с платами должны быть защищены лаком: УР-2З1 или ЭП-7ЗО не менее, чем в 3 слоя.

После подачи напряжения на ИС она переходит в нормальный режим функционирования через время 2 мс и после проведения затем 16 рабочих циклов типа регенерации. Состояние кода адреса А0 при включенном сигнале GAS “0”— для КР565РУ61Д, “1”— для КР565РУ62Д. Регенерация осуществляется по сигналу RAS за 128 циклов перебором адресов А0...А6.

Параметры

| Параметр | 565РУ6В | 565РУ6Г | 565РУ6Д | КР565РУ6Б | КР565РУ6В | КР565РУ6Г | КР565РУ6Д | |

|---|---|---|---|---|---|---|---|---|

Мощность | P | <125 мВт | <125 мВт | <125 мВт | <150 мВт | <140 мВт | <130 мВт | <120 мВт |

Корпус микросхемы | Корпус | 2104.18-1, 201.9-1, 16-QSOP, 201.16-17 | 2104.18-1, 201.9-1, 16-QSOP, 201.16-17 | 2104.18-1, 201.9-1, 16-QSOP, 201.16-17 | 2104.18-1, 201.9-1, 16-QSOP, 2103.16-2 | 2104.18-1, 201.9-1, 16-QSOP, 2103.16-2 | 2104.18-1, 201.9-1, 16-QSOP, 2103.16-2 | 2104.18-1, 201.9-1, 16-QSOP, 2103.16-2 |

Технология изготовления микросхемы | Технология | МДП | ||||||

Серия микросхем | Серия | 565 | ||||||

Семейство логических элементов | Логика | N-МОП | ||||||

Время выборки | TQ | <150 нс | <200 нс | <250 нс | <120 нс | <150 нс | <200 нс | <250 нс |

Организация памяти | Структура | 16k x 1 | ||||||